# Overview of Packaging using Through Silicon Vias (TSV)

CHRIS BARR ECG 721 MEMORY CIRCUIT DESIGN DR. R. JACOB BAKER 12/03/21

## SECTION 1 INTRODUCTION TO THROUGH SILICON VIAS (TSV)

- This section will introduce and discuss through silicon vias and its packaging. Here are some points this section will cover:

- Origin and background of the TSV

- Advantages vs disadvantages of using a TSV

- What devices use TSV's

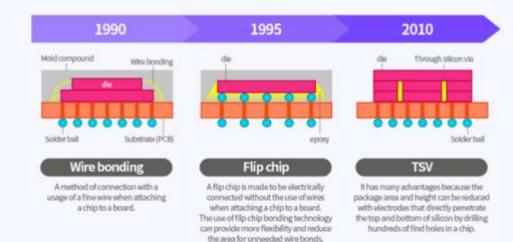

#### THE EVOLUTION OF PACKAGING TECHNOLOGY

Figure 1 Evolution of Integrated Circuits Packaging [18

## **Origin of Through Silicon Vias**

- TSV started with the patent idea of "Semiconductive Wafer and Method of Making the Same" filed on October 23, 1958 (granted on July 17, 1962) by William Shockley. <sup>[15]</sup>

- It was then further developed by IBM researchers Merlin Smith and Stern Emanuel with their patent "Methods of Making Thru-Connections in Semiconductor Wafers" filed on December 28, 1964 (granted September 26, 1967). <sup>[17]</sup>

- It was not until the 1980s that the first 3-Dimensional Integrated Circuit (3D IC) was fabricated with the TSV process. This achieved higher levels of integration with Moore technology – affectively improving performance and cost of semiconductor technology <sup>[2]</sup>.

- Today, many companies use and evolve their technology by implementing 3D TSV packaging into their devices. Some notable companies being Samsung Electronics, Xilinx, and Toshiba Electronics. <sup>[9]</sup> TSV technology is being implemented in both memory and logic silicon devices. <sup>[16]</sup>

Figure 2.1 William Shockley <sup>[12]</sup>

Figure 2.2 Merlin Smith [4]

## About Packaging using Through Silicon Vias

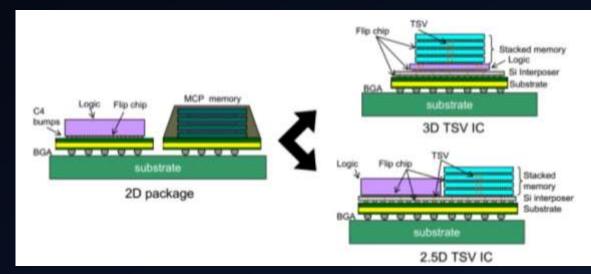

- A TSV is used to allow vertical interconnection access through a microchip and passes through the silicon die or wafer. This allows for stacking of silicon dice. <sup>[20]</sup>

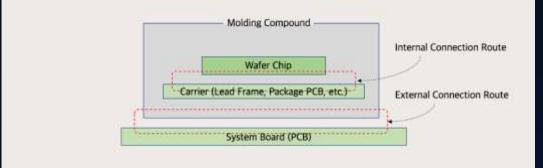

- There are three types of IC packaging

- 1. 2-Dimensional Integrated Circuits (2D IC)

- 2. 2.5-Dimensional Integrated Circuits (2.5D IC)

- 3. 3-Dimensional Integrated Circuits (3D IC)

- TSV's are vital in 2.5-dimensional and 3-dimensional integrated circuits (2.5D and 3D IC) for increasing overall system performance. <sup>[16]</sup>

- Improved power management

- Increased data transfer rates

- Better signal integrity

- Increase in bandwidth

Figure 3 Structure of the three types of IC packaging [1

## About Packaging using Through Silicon Vias

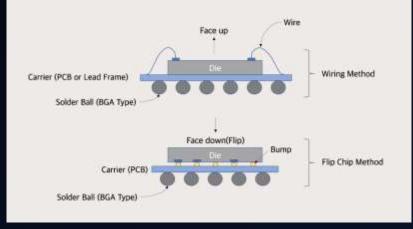

- A 2D IC is packaged using either flip-chip or wire-bond technology. The flip-chip technology is wireless and contains copper tracks, copper vias, and solder bumps that can be roughly 100um in diameter attached to the substrate (PCB). <sup>[10]</sup>

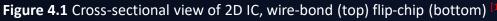

- A 2.5D IC differs from the 2D by adding in a silicon interposer placed between the dice and the substrate, where the interposer has TSV's connecting the metallization layers on its upper and lower surfaces. <sup>[10]</sup> This allows for interconnection between different dice to occur by setting them side-by-side. Example: A memory die to a logic die.

- A 3D IC is set up similarly to 2.5D, but it differs by stacking the dice vertically on top of each other. The TSV's are used to interconnect between the dice.

- Both 2D and 3D IC use flip-chip technique onto the silicon interposer.

Figure 4.2 Cross-sectional view of (a) 3D IC and (b) 2.5D IC [21]

## Advantages and Disadvantages of TSV and Alternatives

This table lists the advantages and disadvantages of packaging using 2D IC (no TSV) and 2.5D and 3D IC (with TSV).

| Integrated Circuits        | Advantages                                                                                                                                                     | Disadvantage                                                                                                                  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 2D<br>(edge-wired package) | <ul> <li>Higher mobilities and immunity<br/>against surface defects</li> <li>More flexible materials can be<br/>used (ex. Making flexible displays)</li> </ul> | <ul> <li>Higher cost</li> <li>Largest layout space</li> <li>Highest power consumption</li> </ul>                              |

| 2.5D<br>(TSV package)      | <ul> <li>Placing chips side-by-side reduces<br/>heat buildup</li> <li>Easier to upgrade/modify</li> </ul>                                                      | <ul><li>Larger layout space</li><li>Larger interconnection</li></ul>                                                          |

| 3D<br>(edge-wired package) | <ul><li>Small layout space used</li><li>Better power consumption</li></ul>                                                                                     | <ul> <li>Slightly larger area used than the<br/>3D TSV package due to edge-wiring</li> <li>Data buffer</li> </ul>             |

| 3D<br>(TSV package)        | <ul><li>Smallest layout space used</li><li>Highest signal performance</li><li>Better power consumption</li></ul>                                               | <ul> <li>Less flexible in various stacked<br/>dice's size, pitch, and material</li> <li>Larger vertical space used</li> </ul> |

Table 1 Advantages and Disadvantages of using different IC packaging [10]

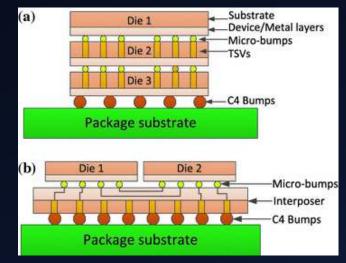

## Importance of Packaging

- Packaging is important in order to prevent the following:

- Physical damage

- Environmental damage

- Lose signal integrity of more sensitive/fragile connections

- And it can also enhance the following:

- Channel heat dissipation

- Improve performance

- Reduce power consumption

- Organizes I/O wires of the IC

Figure 5 Internal and external structure of semiconductor package

### Devices Today using TSV Packaging

Figure 6.1 DRAM using 3D TSV packaging technology

- DDR5 SDRAM made by Kingston

- Package Type: BGA, 3DS TSV

- Kintext UltraScale made by Xilinx

- Package Type: SSI (3D TSV)

Figure 6.2 FPGA using 3D TSV packaging technology [2

- DDR4 RDIMMs made by Samsung

- Package Type: BGA, 3DS TSV

Figure 6.3 RDIMM Chip using 3D TSV packaging technology [14]

#### SECTION 2 ANALYTICS OF THROUGH SILICON VIAS (TSV) AND ITS PACKAGING

- This section will go more indepth with TSV technology. Here are some points this section will cover:

- Performance

- Cost

- Using BGA in TSV IC technology

- Process of a TSV

- Current problems in TSV

technology

- Future outlook of TSV packaging

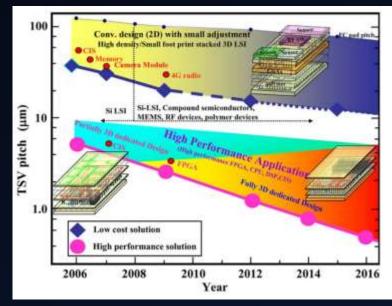

Figure 7 Road map of TSV technology [11]

#### Performance of TSV Packaging

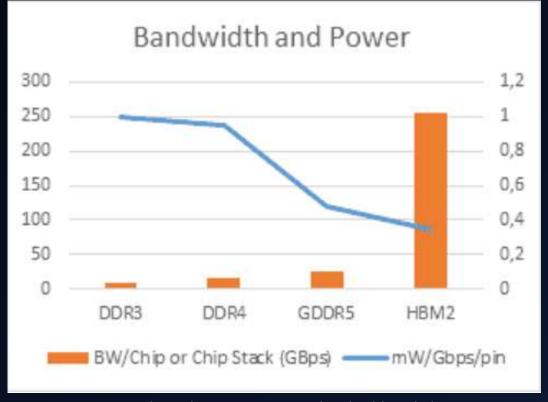

- From the older DDR3 to the newer HBM2, there's a significant increase in performance for both signal performance and power consumption as shown in Figure 8.

- <u>Note</u>: The right-side y-axis in Figure 8 is supposed to have a decimal, not a comma.

- The DDR3, DDR4, and GDDR5 devices recorded in the graph were that of 2D IC technology. This graph showcases the improvement by migrating to the more evolved technology, 3D TSV.

- By combining flip-chip ball grid array (FCBGA) assembly with 3DS TSV technology, the performance of HBM2 can be realized. <sup>[16]</sup>

**Figure 8** Memory products showcasing increase bandwidth with decrease in power consumption <sup>[16]</sup>

Bandwidth (GBps) left axis, Power Consumption (mW) per Gbps per pin right axe

## Cost of TSV Packaging

- With increase performance comes evolving technology. The 3D TSV IC is currently the new generation of IC tech.

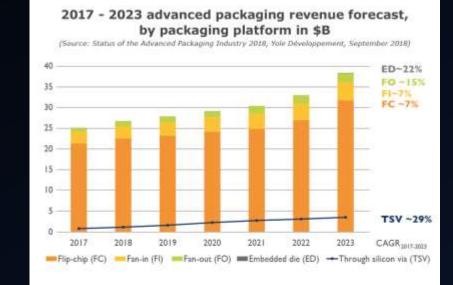

- In Figure 9.1, the CAGR of TSV packaging has increased a lot more than its other packaging competitors. This shows that there is an increasing larger demand for TSV packaging in the recent years than there are for alternatives. <sup>[7]</sup>

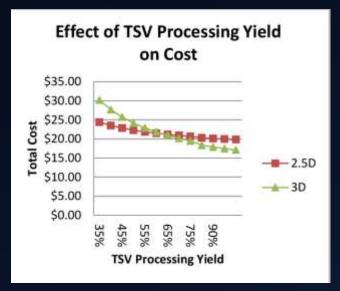

- In Figure 9.2 assesses the cost between 2.5D and 3D TSV technology. The evolving 3D TSV technology grows to be cheaper over time.

**Figure 9.1** Compound Annual Growth Rate (CAGR) of Advanced Packages in the last few years <sup>[7]</sup>

Figure 9.2 Cost Comparison of 2.5D and 3D TSV [13]

## BGA Technology (flip-chip) in TSV Packaging

Most popular TSV IC's use BGA technology, or flip-chip, to maximize performance of their devices. Here are some advantages and disadvantages of using a BGA.

| Advantages                                    | Disadvantages                             |

|-----------------------------------------------|-------------------------------------------|

| High interconnection density                  | Prone to stress due to<br>flexural stress |

| Efficient (fast) and manageable               | Difficult inspection for verification     |

| Better heat dissipation                       | Cost of equipment (oven)                  |

| Shorter path between die<br>and PCB substrate | Difficult to modify during development    |

Table 2 Advantages and Disadvantages of using BGA [2

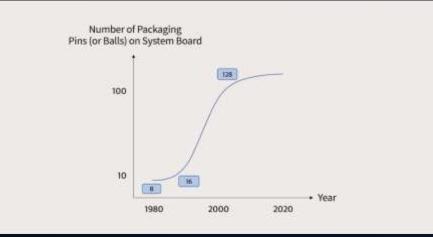

Figure 10 Increase of BGA pins as IC's evolve

## In-depth look at a TSV Process

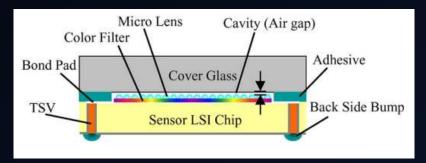

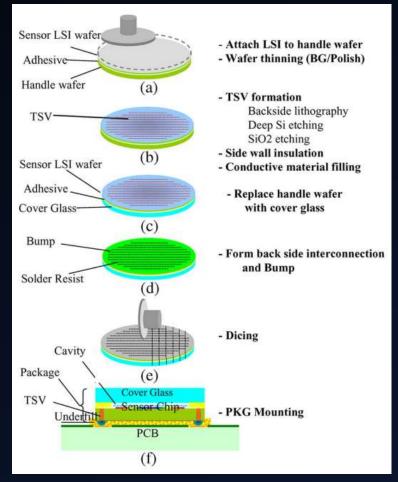

- Figure 11 is a 3D Large-Scale Integration (LSI) structure that uses TSV technology to interconnect the image sensor.

- Image sensors were one of the first applications to use TSV's.

- In this specific project, they use TSV's to connect the backside bump to the sensor chip, allowing direct connect to the substrate (PCB).

- The TSV holes are made with a deep Si etch and a successive SiO<sub>2</sub> etch process. A rectangular etch is made for the TSV once created.

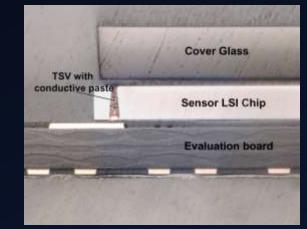

Figure 11.2 Cross-sectional view of CSP Structure [11]

**Figure 11.1** Chip Sized Package (CSP) for an Image Sensor Process flow with TSV <sup>[11]</sup>

#### In-depth look at a TSV Process

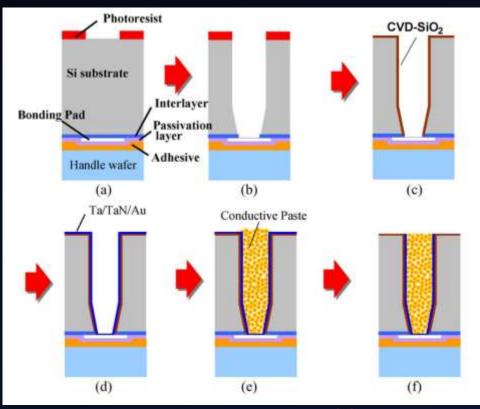

- 1. The TSV goes through the etching process, forming a cavity. Figure 12 (a)(b).

- A side-wall insulator is formed by using a low temperature plasma enhanced chemical vapor deposition (PECVD), SiO<sub>2</sub> deposition, and SiO<sub>2</sub> RIE. This is made to create a dielectric insulation to prevent current leakage. Figure 12 (c).

- 3. Contact and diffusion barrier metal deposition are placed in the TSV cavity. Figure 12 (d).

- 4. The cavity is now filled with a conductive paste. This is used to reduce process cost. Figure 12 (e).

- The top of the TSV is shaved off of excess contact metal, conductive paste, and diffusion metal. Figure 12 (f).

Figure 12 Process flow for a TSV [11]

#### In-depth look at a TSV Process

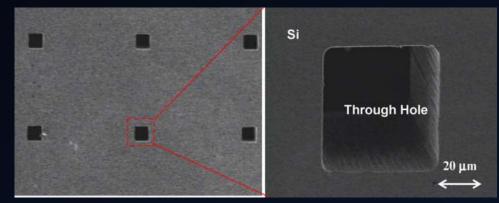

- Figure 13.1 was scanned using an electron microscope (SEM) to capture this image. This image is showing an etched rectangular TSV cavity of 60 x 60 um<sup>2</sup>.

- Figure 13.2 gives the cross-sectional view after the TSV process was completed. The TSV has a diameter of 20 um and depth of 270um.

- Advantages of using this method for creating TSV's:

- Lower cost of equipment compared to other techniques

- Shorter processing time

- Disadvantages of using this method for creating TSV's:

- TSV's have relatively high resistivity than normal

- Conductive paste contraction during the cure cycle

Figure 13.1 TSV hole created after the etching process [11

Figure 13.2 Cross-sectional view of CSP after packaging [1

## Current Challenges of TSV Packaging

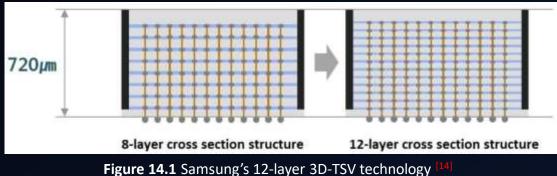

- As 3DS TSV ICs continue to grow, devices as large as 12 stacks of die are being created. <sup>[14]</sup> Samsung's 12-layer 3D-TSV IC technology has a vertical height of 720um. Consider the three-way optimization: power, performance, and area (PPA). With the traditional 2D IC slowly turning towards 3D, cubic area must be optimized. <sup>[8]</sup> As of now, with every 3DS TSV IC, the increase in <u>vertical area</u> is the tradeoff.

- One of the bigger hurdles are <u>power and thermal</u>. The top die of a 3DS IC gets its power from a lower die. At the lowest die, it gets its power from the interposer. The higher the stack, the more power is consumed from the lowest die footprint. And the more power applied to the footprint, the more power needs to be dissipated. <sup>[8]</sup>

- Currently not many <u>EDA tools support 3D IC development</u>. EDA tools need to keep up with the 3DS IC designs to incorporate vertical stacking tradeoffs, alongside its power consumption, so it can meet PPA standards. <sup>[8]</sup>

## Moving Forward

- More dice will stack together like Samsung's new 12-layer 3D-TSV. Thickness remains the same thickness as its 8-layer counterpart (720um). <sup>[14]</sup>

- Provides 24-gigabyte (GB) of High Bandwidth Memory (HBM)

- Over 60,000 TSV holes for maximum performance

- Currently, 3DS ICs are used primarily on memory-based products. Other future applications may lead into further development of Internet-of-Things (IoT) and mobile devices. <sup>[23]</sup>

#### Summary

- A TSV is used as a high-performance interconnection technique to fabricate three-dimensional integrated circuits (3D IC). It stands as the higher performing technology as opposed to its alternatives: wire-bond, flip-chip.

- There are three different design types in IC (1) 2-dimensional, (2) 2.5-dimensional, and (3) 3-dimensional. TSVs are vital in 2.5D and 3D designs, but both use flip-chip to attach the chip to the substrate (PCB).

- The benefits of using 2.5D and 3D TSV technology is the improved power management, increased data transfer rates, better signal integrity, and the increase in bandwidth.

- The drawbacks of using 2.5D and 3D TSV technology is the larger vertical space used and the flexibility of dice size, pitch, and materials used.

- The packaging of the IC is important to prevent damage and improve chip efficiency/performance.

- 3DS TSV IC demand are on the rise and will soon see the technology used more often to improve electronics cost and performance.

#### References

- 1. Castellano, R. (2017, June 19). Advanced Semiconductor packaging starting to change memory market landscape. Advanced Semiconductor Packaging Starting To Change Memory Market Landscape. Retrieved from https://seekingalpha.com/article/4082455-advanced-semiconductor-packaging-starting-to-change-memory-market-landscape.

- 2. Das, S. (2017, March 9). BGA advantages and disadvantages. BGA Advantages and Disadvantages-Blog-Jaapson blog and resource center. Retrieved from http://www.jps-pcb.com/blog/BGA-Advantages-and-Disadvantages.html.

- 3. ETHW. (n.d.). Merlin G. Smith. Merlin G. Smith Engineering and Technology History Wiki. Retrieved from https://ethw.org/Merlin\_G.\_Smith.

- 4. Guo, X., Xue, Z., & Zhang, Y. (2019, December). (*PDF*) manufacturing of 3D multifunctional microelectronic ... Manufacturing of 3D multifunctional microelectronic devices: challenges and opportunities. Retrieved from https://www.researchgate.net/publication/333914877\_Manufacturing\_of\_3D\_multifunctional\_microelectronic\_devices\_challenges\_and\_opportunities.

- 5. Jin, J.-moon. (2021, May 6). "light, thin, short and small", the development of semiconductor packages. Retrieved from https://news.skhynix.com/light-thin-short-and-small-the-development-of-semiconductor-packages/.

- 6. Kingston Technology Company. (2021, October). DDR5 memory standard: An introduction to the next generation of DRAM module technology Kingston Technology. DDR5 Memory Standard: An introduction to the next generation of DRAM module technology. Retrieved from https://www.kingston.com/unitedstates/us/memory/ddr5-overview.

- 7. Kumar, S. (2018, September 27). Advanced packaging rides at the forefront of the semiconductor industry surge i-micronews. Advanced packaging rides at the forefront of the semiconductor industry surge. Retrieved from https://www.i-micronews.com/advanced-packaging-rides-at-the-forefront-of-the-semiconductor-industry-surge/.

- 8. Larsen, K. (2021, September 28). 3D IC: Opportunities, challenges, and solutions. Semiconductor Engineering. Retrieved from https://semiengineering.com/3d-ic-opportunities-challenges-and-solutions/.

- 9. MarketWatch. (2021, November 22). Global 3D TSV package market 2021 upcoming trends, Latest Innovation, advance technology and top companies to 2027. Global 3D TSV Package Market 2021 Upcoming Trends, Latest Innovation, Advance Technology and Top Companies to 2027. Retrieved from https://www.marketwatch.com/press-release/global-3d-tsv-package-market-2021-upcoming-trends-latest-innovation-advance-technology-and-top-companies-to-2027-2021-11-22.

- 10. Maxfield, M. (2012, April 8). 2D vs. 2.5D vs. 3D ICS 101. EETimes. Retrieved from https://www.eetimes.com/2d-vs-2-5d-vs-3d-ics-101/.

- 11. Motoyoshi, M. (2009, September 24). Paper through-siliconvia(tsv) emlab.uiuc.edu. Through-Silicon Via (TSV). Retrieved from http://emlab.uiuc.edu/ece546/appnotes/tsv/Yokohama\_paper.pdf.

- 12. Nobel Prize Outreach AB. (n.d.). The nobel prize in physics 1956. NobelPrize.org. Retrieved from https://www.nobelprize.org/prizes/physics/1956/shockley/facts/.

- 13. Palesko, C., Palesko, A., & Vardaman, E. J. (1970, January 1). [*PDF*] cost comparison of 2.5D/3D packaging to other packaging technologies: Semantic scholar. Cost Comparison of 2.5D/3D Packaging to Other Packaging Technologies. Retrieved from https://www.semanticscholar.org/paper/Cost-Comparison-of-2.5D%2F3D-Packaging-to-other-Palesko/c86c8dc436b2063b0b5687039856caf74e642a54.

- 14. Samsung Global Newsroom. (n.d.). Samsung Electronics develops industry's first 12-layer 3D-TSV Chip Packaging Technology. Samsung Electronics Develops Industry's First 12-Layer 3D-TSV Chip Packaging Technology. Retrieved from https://news.samsung.com/global/samsung-electronics-develops-industrys-first-12-layer-3d-tsv-chip-packaging-technology.

- 15. Shockley, W. (1962, July 7). Semiconductive Wafer and Method of Making the Same.

- 16. Silvestri, P., Alapati, R., & Kelly, M. (2018, September 3). Choose through silicon via (TSV) packaging for improved performance. Choose Through Silicon Via (TSV) Packaging for Improved Performance. Retrieved from https://anysilicon.com/choose-silicon-via-tsv-packaging-improved-performance/.

- 17. Smith, M. G., & Emanuel, S. (1967, September 26). Methods of making thru-connections in semiconductor wafers.

- 18. Son, H.-Y. (2021, July 21). Advanced Packaging Technologies overcoming the memory system performance and capacity limitation. Retrieved from https://www.eetimes.com/advanced-packaging-technologies-overcoming-the-memory-system-performance-and-capacity-limitation/.

- 19. Sperling, E., & Lapedus, M. (2019, March 22). Making chip packaging simpler. Retrieved from https://semiengineering.com/making-chip-packaging-simpler/.

- 20. Techopedia. (2014, November 11). What is a through-silicon via (TSV)? definition from Techopedia. Techopedia.com. Retrieved November 30, 2021, from https://www.techopedia.com/definition/30421/through-silicon-via-tsv.

- 21. Xie, Y. (2017, January 5). 3D/2.5D IC-based obfuscation link.springer.com. Retrieved from https://link.springer.com/chapter/10.1007/978-3-319-49019-9\_12.

- 22. Xilinx. (2021). 3D ICS. Retrieved from https://www.xilinx.com/products/silicon-devices/3dic.html.